# ALGORITHMS OF FUNCTIONAL LEVEL TESTABILITY ANALYSIS FOR DIGITAL CIRCUITS<sup>1</sup>

Raimund UBAR\* and Ktzysztof KUCHCINSKI\*\*

\*Tallinn Technical University Ehitajate tee 5

EE-0108 Tallinn Estonia

\*\*Krzysztof KUCHCINSKI Linköping University

S-58183 Linköping Sweden

Received: May 13, 1992

### Abstract

A general approach is proposed for calculating controllabilities and observabilities of signals in sequential and combinational circuits at the functional level. The methods and algorithms are based on alternative graphs which are an extension of binary decision diagrams. The algorithms are general and can be easily adjusted for calculation of different testability measures.

Keywords: digital circuits, finite state machines, testability measures, alternative graphs, probabilistic approach.

# Introduction

The design of testable digital circuits heavily relies on testability measures which aid designer to reduce both the test generation complexity and the test length. As digital circuits become more complex, efficiency and adequacy of testability analysis will progressively gain more significance. Recent approaches (CHEN and MENON, 1989; HAMIDA and KAMINSKA, 1991) are directed to develop new methods for testability analysis at the functional level. Their goal is, however, not totally accomplished. In (CHEN and MENON, 1989), calculating testability measures is not a uniform procedure for different parts of circuits. For combinational circuits, binary decision diagrams and for sequential circuits, state transition tables are used. In (HAMIDA and KAMINSKA, 1991) an attempt is made to treat these classes of circuits uniformly, but only a subclass of sequential circuits with a single loop is discussed. In this paper, two types of new results are presented. First, a new method for testability calculus based on alternative graphs (UBAR, 1976; UBAR, 1983; UBAR and KUCHCINSKI, 1988) is proposed. The method is applicable for combinational and sequential circuits

<sup>&</sup>lt;sup>1</sup>This work has been partially supported by the Swedish Institute, Stockholm

and for the general class of finite state machines with arbitrary number of feedbacks rather than sequential circuits with only a single loop. Unlike the previous functional approaches, digital circuits can be described at higher level than Boolean functions. Instead of only Boolean, also integer variables and functions are used. Second, some generalizations are proposed and relationships between different testability measures are established. It is shown that testability measures cannot be treated as absolute measures because they are very tightly related to a testing method used. For instance, they have different meaning for deterministic and random testing approaches. In the case of deterministic testing we can speak about two types of tests: linear test sequences (unconditional testing) and test sequences with loops (conditional testing). For both of these cases, as testing will be carried out by different strategies, also testability has to be calculated in different ways. In the current literature, no such differentiation of testability measures and calculation methods has been made. Based on this, a hierarchy of sequential controllabilities for different types of testing is established where controllabilities for random testing are based on controllabilities for conditional testing and these in their turn, are based on controllabilities of unconditional testing.

A general formula for representing combinational controllability is proposed where the estimations of initiability and other controllability measures such as probabilistic and heuristic ones, can be regarded as its components. It is also shown that the newly introduced initiability measure (HAMIDA and KAMINSKA, 1991) is a special case of the probabilistic controllability. Hence, it is not needed to handle the initiability as a separate measure of testability with its own dedicated calculation methods. Instead, it can be treated as a component of the controllability and it can be calculated in the same way as the controllability is calculated.

### Alternative Graphs and Digital Circuits

Alternative graphs ( $\mathcal{AG}$ ) were introduced in (UBAR, 1976; UBAR, 1983) for test design purposes for digital circuits and systems.  $\mathcal{AG}$  is defined as a rooted noncyclic directed graph whose nodes are labelled by variables, constants or algebraic expressions. The variables (constants) can be of different types, i. e. they can have values from different finite sets of values. For each nonterminal node, a one-to-one correspondence exists between the current value of the node variable (expression) and an output arc. According to the value of the node variable, always one and only one output arc is activated. A path in an  $\mathcal{AG}$  is activated if all arcs forming the path are activated. The  $\mathcal{AG}$  is activated to a value k if there exists an activated path which includes both the root node and the terminal node labelled by the constant k (or expression with value k). An alternative graph  $\mathcal{G}_y$ represents a digital function y = f(x), where  $x = (x_1, x_2, \ldots, x_n)$ , if for each pattern of x (for each set of values of components  $x_i$ ) the  $\mathcal{AG}$  will be activated to the value which is equal to y.

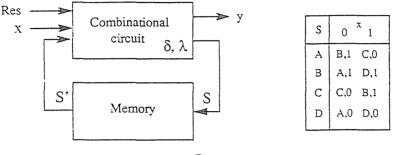

Fig. 1.

A digital circuit is considered as a system of digital functions y = f(x) which describe the behavior of components (subcircuits) of the circuit. Sequential components (*Fig. 1*) of the circuit are represented by transition functions  $S = \delta(Res, x, S')$  and output functions  $y = \lambda(x, S)$  where S denotes the state variable having, in general case, integer values (S' represents the previous value of the state variable). Since all functions f can be represented by  $\mathcal{AG}s$  every digital circuit can be represented by a system of  $\mathcal{AG}s$ .

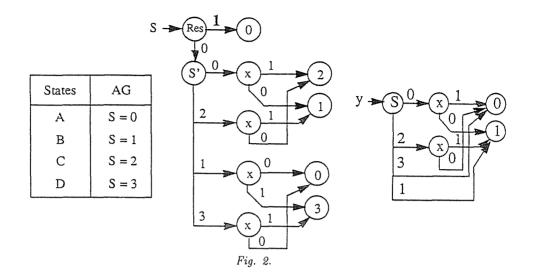

Let us consider a finite state machine (FSM) in Fig. 1 used as an example in (CHEN and MENON, 1989) and the corresponding  $\mathcal{AG}$ -representation in Fig. 2. Here,  $\mathcal{G}_y$  and  $\mathcal{G}_s$  represent  $\mathcal{AG}s$ , correspondingly, the output and transition functions of the FSM, where the values S=0, 1, 2, 3 correspond to the states A, S, C, D of the FSM, correspondingly.

The representation of digital circuits by  $\mathcal{AG}s$  gives an advantage to have the possibility of representing the cause-effect relationships in a simple and direct form. This representation is important from the point of view of the controllability and observability calculation. Using integer variables for representing states (and, possibly, inputs and outputs), allows a compact representation of FSMs by  $\mathcal{AG}s$ .

### **Combinational Controllability**

Combinational controllability CC(y=k) of a signal y in a digital circuit to a specific value k can be regarded as the probability P(y=k) y has the value k (CHEN and MENON, 1989). The computation of P(y=k) on alternative

graphs is based on traversing paths in  $\mathcal{G}_y$  using probabilities P(x = j)for node variables x on activated paths. The probability of traversing an arc activated by the value x = j is equal to the probability P(x = j). Assuming that the input variables of the digital circuit are independent, the probability P(p) of traversing any path p in  $\mathcal{AG}$  is given by the product of the traversal probabilities of all arcs in the path. In the case of not independent variables, the result will be the lower bound of the probability. The probability (or its lower bound) of producing the value y = k is equal to the sum of probabilities of traversing paths that end in a terminal node which has the value k. From above the following algorithm for calculating CC(y=k) on the basis of  $\mathcal{G}_y$  results:

#### Algorithm 1

- 1. Find all paths p from the root up to the terminal nodes m where c(m) = k.

- 2. Calculate for all paths p the probabilities P(p).

- 3. Calculate  $CC(y=k) = \sum_{p} P(p)$ .

In the case when the variables in expressions are not input variables, the algorithm must be executed recursively. The algorithm can be used uniformly for combinational and sequential circuits. Both calculations of CC(y = 1) and CC(S = 3) are carried out identically. We do not treat differently the case of combinational part (when calculating CC(y = 1)) and the case of sequential part of the device (when calculating CC(S=3)). However, there is a difference related to the possible loops which require a recursive use of the Algorithm 1. The problem of handling loops is discussed in (UBAR and KUCHCINSKI, 1992).

## Example 1

Assume: P(Res=0) = 0.8; P(Res=1) = 0.2; P(x=0) = P(x=1) = 0.5.

a) CC(S = 0) = P(S = 0) = P(Res = 1) + P(Res = 0)[P(S = 1)P(x = 0) + P(S=3)P(x=0)], CC(S=1) = P(S=1) = P(Res=0)[P(S=0)P(x=0) + P(S=2)P(x=1)], CC(S=2) = P(S=2) = P(Res=0)[P(S=0)P(x=1) + P(S=2)P(x=0)],CC(S=3) = P(S=3) = P(Res=0)[P(S=1)P(x=1) + P(S=3)P(x=1)],

which has the following solution:

| CC(S=0)=0.37; |

|---------------|

| CC(S=1)=0.24; |

| CC(S=2)=0.24; |

| CC(S=3)=0.15. |

b) CC(y=1) = P(y=1) = P(S=0)P(x=0) + P(S=2)P(x=1) + P(S=1) = 0.55.

The algorithm described is very general and can be easily modified to calculate other testability measures. For example, to implement the SCOAP algorithm (GOLDSTEIN, 1979), it is enough to substitute the step 2 by computation  $CC_p = \sum \{CC(x)\}$  over all variables x encountered on the path p and the step 3 by computation of  $CC(y) = \min\{CC_p\}$  over all p. Differently from traditional cases, it is not needed to update the library of circuit components when new testability measures are introduced, to describe calculation procedures for components.

Consider the probabilistic controllability function (discussed in CHEN and MENON, 1989) as a composition:

$$CC(y = k) = P(y = k) = P_{S}(y = k) + P_{P}(y = k) + P_{L}(y = k),$$

where  $P_s$ ,  $P_P$  and  $P_L$  denote the probabilities of setting y to k, correspondingly, by the shortest sequence, by one of the all possible sequences without loops except the shortest one, and by all possible sequences that contain loops. From this expression, different measures like initiability (HAMIDA and KAMINSKA, 1991) as  $P_s + P_P$ , probabilistic measure (lower bound) as  $P_P$ , and heuristic measures similar to (GOLDSTEIN, 1979) result as special cases which can be calculated by Algorithm 1 and do not need other dedicated procedures (UBAR and KUCHCINSKI, 1992).

#### **Combinational Observability**

The observability of the variables of a digital circuit is a function of both the observability and controllability of other variables. Traditionally, at the binary level for explaining the observabilities, a Boolean differential calculus is used.  $\mathcal{AG}$ s allow a simple extension of Boolean derivatives for higher level digital functions.

Combinational observability CO(y, x) of a signal x through another signal y is the probability P(dy/dx) that a change in a signal x will cause a change in an observable signal y. The computation of P(dy/dx) is similar to the procedure of calculating Boolean derivatives on  $\mathcal{AGs}$  (UBAR, 1976). Note that the value of the derivative dy/dx for the case where y and xare integer variables is still binary. For a digital function y = f(x) where y and x are integer variables, we shall have dy/dx = 1, if and only if an arbitrary change of the value of x evokes an arbitrary change in the value of y. To find solutions for the differential equation dy/dx = 1, we can use the following algorithm based on  $\mathcal{AGs}$ :

Algorithm 2

- 1. Activate a path  $p_0$  in the graph  $\mathcal{G}_y$  from the root up to a node m which is one of the nodes that are marked by the variable x;

- 2. Activate two arbitrary nonoverlapping paths  $p_i$  and  $p_j$  from the node m up to different terminal nodes  $m_i$  and  $m_j$ , so that the condition  $c(m_i) \neq c(m_j)$  holds.

Note that the activated paths  $p_0$ ,  $p_i$  and  $p_j$  must be nonoverlapping. In general case, there could be more than one node m marked by x. For solving the equation dy/dx = 1, it will be enough to find the solution using only one of these nodes. For calculating CO(y, x), we have to consider all nodes in  $\mathcal{AG}$ , marked by x:

#### Algorithm 3

- 1. Activate for all nodes m, marked by x, the groups of paths  $GR_m = (p_0, p_i, p_j)_m$ .

- 2. Calculate the probabilities  $P_m = P(p_0)P(p_i)P(p_j)$  of simultaneously activating paths  $p_0$ ,  $p_i$  and  $p_j$  for all groups found in the 1st step.

- 3. Find  $CO(y, x) = \sum_{m} P_m$ .

Example 2

CO(y, x) = P(dy/dx) = P(S=0) + P(S=2) = 0.37 + 0.24 = 0.61,CO(y/S=3) = P(dy/d(S=3)) = P(S=1) + P(S=2)P(x=1) + P(S=0)P(x=0) = 0.55.

# Deterministic Sequential Controllability for Unconditional Testing

In the following, uniform algorithms for calculating sequential controllabilities (SC) for combinational and sequential parts of digital circuits represented at functional level are proposed. Sequential testability measures are dependent on the testing method (environment) used. For instance, they have different meaning for unconditional, conditional and random testing approaches. Hence, the corresponding types of SCs are introduced: deterministic SC, probabilistic SC for conditional testing and probabilistic SCfor random testing.

Let us assume the following commonly accepted definition (GOLD-STEIN, 1979; CHEN and MENON, 1989; HAMIDA and KAMINSKA, 1991): sequential controllability SC(y = k) of a signal y in a digital circuit for a specific value k is measured as an estimated length of a test sequence (number of time frames) needed for setting the signal to that value; SC of primary inputs is estimated as 1, which indicates that a sequence of length 1 is sufficient to set the value.

Consider the deterministic (unconditional) sequential controllability SCD(y = k) of a signal y, represented by a function y = f(x), as the minimum length of a sequence needed to set y to the value k. In general case, to set a line y to a value k, the path in  $\mathcal{G}_y$  which terminates in a node labelled by the constant k must be activated. To activate this path, all variables in the path must be set to the needed values. In order to compute the SC of the activation of this path, SCs for all the signal values related to that activation are needed.

controlled independently, the SC associated with activation of the given path can be, analogonsly to (CHEN and MENON, 1889), estimated as the maximum of SCs of signals involved. The sequential controllability of the signal y may be defined as the minimum of the sequential controllabilities of activation of all possible paths in the  $\mathcal{AG}$  that produce the desired value k. This leads directly to the following algorithm.

## Algorithm 4

- 1. Find all paths p from the root node up to the terminal nodes m where c(m) = k.

- Find, for all paths p, L(p) = max{SCD(x(m))+L<sub>p</sub>} where SCD(x(m)) is the controllability associated with the node variable x(m) encountered on the path p, and L<sub>p</sub> is the length unit or time frame (L<sub>p</sub>=1 if x(m) is a state variable and p belongs to the AG of the state variable, and L<sub>p</sub>=0 otherwise).

- 3. Calculate  $SCD(y = k) = \min\{L(p)\}$  over all paths p with terminal value k.

# Example 3

Two important results related to this section have to be noted. First, Algorithm 4 is similar to Algorithm 1. Both algorithms consist of three parts: tracing paths in  $\mathcal{AG}s$ , calculating a function along these paths and calculating a function over all paths. The difference between the algorithms is in functions to be calculated. Hence, we can conclude that  $\mathcal{AG}s$  give the possibility to develop uniform procedures for computing combinational and sequential controllabilities.

Second, Algorithm 4 is uniform for calculating different controllability measures. It can be easily modified for computing new measures by modifying functions calculated in the 2nd and 3rd steps. For example, instead of minimum, the average function could be calculated or, instead of maximum, analogously to the SCOAP (GOLDSTEIN, 1979), the sum could be used.

# Probabilistic Sequential Controllability for Conditional Testing

The approach considered in this section is similar to (CHEN and MENON, 1989), except that instead of different methods for combinational and sequential parts of the circuit, a uniform algorithm for both parts will be given. Regard the probabilistic sequential controllability SCP(y = k) of signal y, represented by a function y = f(x), as the statistical average length of a sequence needed to set y to the value k in the case when an initial state of the system is unknown. The calculation procedure is based on the state probabilities P(S=i) computed by Algorithm 1, and the conditional deterministic sequential controllabilities SCD(y=k/S=i) to set y to the value k if the state of the FSM is S=i. For calculating SCD(y=k/S=i) we propose the following algorithm.

### Algorithm 5

- 1. Find a path p from the root in  $\mathcal{G}_y$  with the restriction S=i up to the terminal node m, where c(m)=k.

- 2. Compute  $L(p) = \max\{SCD(x(m)) + L_p\}$ , where SCD(x(m)) is the controllability associated with the node variable x(m) encountered in the path p (except the state variable S).

- 3. If no such a path exists in  $\mathcal{G}_y$ , find all paths  $p_p$  in  $\mathcal{G}_s$  through S = iup to terminal nodes m with corresponding values  $c(m) = k_p$  and compute for all p,  $L(p) = \max\{SCD(x(m))+L_p\}+SCD(y=k/S=k_p)$ .

- 4. Calculate  $SCD(y=k) = \min\{L(p)\}$  over all paths p that were found.

Calculation of the controllability SCP(y=k) will be produced by the following expression:  $SCP(y=k) = \sum_{i} \{P(S=i)SCD(y=k/S=i)\}.$

Example 4

Assume: SCD(x=k)=1 for arbitrary values of k if x is the input variable. SCD(y=0/S=0) = SCD(x=1)=1,  $SCD(y=0/S=1) = \min\{\{SCD(x=0)+SCD(y=0/S=0)\},$   $\{SCD(x=1)+SCD(y=0/S=3)\}\}=2,$  SCD(y=0/S=2) = SCD(x=0)=1,SCD(y=0/S=3) = 1.

Using the results from Example 1, we get:

$$SCP(y=0) = (0.37 \cdot 1) + (0.24 \cdot 2) + (0.24 \cdot 1) + (0.15 \cdot 1) = 1.24$$

By analogy:

$$SCP(y = 1) = 1.15;$$

$SCP(S = 0) = 1,$   $SCP(S = 1) = 1.2;$

$$SCP(S = 2) = 1.2;$$

$SCP(S = 3) = 1.7.$

Note that the values of SCP(S = i) for i = 1, 2, 3 are smaller than the values of SCD(S = i) because the control sequence for the case of SCP will be conditional and the current state can be observed and the shortest sequence for this state can be chosen. For the case of SCD, the information of the current state is not available, and the control sequences have to be general, independent of the current state.

## Probabilistic Sequential Controllability for Random Testing

Opposed to the previous probabilistic approach, where a mixture of deterministic and probabilistic information was used, in the random testing approach, we shall use only probabilities of current states and probabilities of all possible sequences.

Regard the probabilistic sequential controllability SCR(y=k) of signal y, represented by a function y = f(x), as the statistical average length of a sequence needed to set y to the value k in the case when the initial state of the system is unknown and all input patterns are random. The calculation procedure is based on the state probabilities P(S=i) computed by Algorithm 1, and the conditional probabilistic sequential controllabilities SCP(y=k/S=i) to set a value k to the variable y if the state of the FSM was S=i. For calculating SCP(y=k/S=i) we propose the following algorithm.

## Algorithm 6

- 1. Find all possible paths p in  $\mathcal{G}_y$  (with the restriction S = i) up to terminal nodes m with the value  $c(m) = i_p$ .

- 2. Calculate the probabilities P = P(p) for all paths p over all variables (as in Algorithm 1) except the state variable (P = 1, if no variables other than the state variable are met).

- 3. If  $i_p \neq i$ , find the value j of the terminal node for the simultaneously with p activated path  $p_j$  in  $\mathcal{G}_s$  and calculate  $P = P(p_j)$  as in the step 2.

- 4. Calculate the weighted length  $L_p = P_p \cdot (L+l)$  of the sequence for all p corresponding to this path, where recursively  $L = P \cdot SCP(y = k/S = j)$  if  $i_p \neq i$ , otherwise L=0, and l=1 if y is the state variable, otherwise l=0.

- 5. Find  $SCP(y=k/S=i) = \sum_{p} L_{p}$ .

Calculation of the controllability SCR(y = k) will be produced by the following expression:  $SCR(y=k) = \sum_{i} \{P(S=i)SCP(y=k/S=i)\}.$

# Example 5

On the basis of the Algorithm 6 we find a system with 4 equations for calculation of SCR(y=0) and a system of three equations for calculation of SCR(S=0). These systems of equations together with solutions are presented below.

$$\begin{split} SCP(y=0/S=0) &= & [P(x=1) \cdot 0] + [P(x=0) \cdot (SCP(y=0/S=1)+1)] = \\ & 1.33; \\ SCP(y=0/S=1) &= & 1 \cdot \{[P(x=0) \cdot (SCP(y=0/S=0)+1)] + [P(x=1) \cdot (SCP(y=0/S=3)+1)]\} = 1.66; \\ SCP(y=0/S=2) &= & [P(x=0) \cdot 0] + [P(x=1) \cdot (SCP(y=0/S=1)+1)] = \\ & 1.33; \\ SCP(y=0/S=3) &= & 1 \cdot 0 = 0 \\ SCP(S=0/S=1) &= & P(Res=1) + P(Res=0) \{P(x=0) + \\ & P(x=1)[SCP(S=0/S=3)+1]\} = 1.68; \\ SCP(S=0/S=2) &= & P(Res=1) + P(Res=0) \{P(x=0) + \\ & [SCP(S=0/S=2) + P(Res=1) + P(Res=0)] \{P(x=0) + \\ & [SCP(S=0/S=2) + 1]\} = 1.68; \\ SCP(S=0/S=3) &= & P(Res=1) + P(Res=0) \{P(x=1) + \\ & [SCP(S=0/S=2) + 1]\} = 2.78; \\ SCP(S=0/S=3) &= & P(Res=1) + P(Res=0) \{P(x=1) + \\ & P(x=1)[SCP(S=0/S=3) + 1]\} = 1.7. \end{split}$$

Using the results of Example 3 (for SCR(S=0) normalizing the probabilities):  $SCR(y=0) = (0.37 \cdot 1.33) + (0.24 \cdot 1.66) + (0.24 \cdot 1.33) = 1, 21;$  $SCR(S=0) = [(0.24 \cdot 1.68) + (0.15 \cdot 1.7) + (0.24 \cdot 2.78)]/0.63 = 2.1.$

Similarly, we get SCR(S=2) = 5.0 and SCR(S=3) = 6.87. Note that the values of SCR will be generally higher than the values of SCP because the control sequence for the case of SCR will be fully probabilistic whereas in the case of SCD, the current state can be observed and the shortest sequence for this state can be chosen.

# Sequential Observabilities

Sequential observability SO(y, x) is an estimation of the number of time frames required to propagate the effects of a signal change on a line x to a primary output y. As in the case of combinational observability we assume that the change to be propagated occurs only in a single time frame. In this case, it is easy to modify the Algorithm 3 as follows.

Algorithm 7

- 1. Activate for all nodes m, marked by x, the groups of paths  $\mathcal{G}R_m = (p_0, p_i, \dots, p_j)_m$ .

- 2. Calculate  $M_m = \max\{SC(p_0), SC(p_i), SC(p_j)\}_m$  for all groups found in the 1st step, where SC(p) is the maximum of sequential controllabilities of signal values needed for activation of the path p.

- 3. Find  $SO(y, x) = \min\{M_m\}$ .

From Algorithm 7, it clearly follows that the sequential observability is a function of sequential controllabilities. Hence, in the same way, as we classified controllabilities into different types, the same classification can be carried out with observabilities. The type of controllability used in Algorithm 7, directly defines the type of the observability calculated. So, referring to Section 4, we can differentiate the deterministic sequential observability SOD, the probabilistic sequential observability SOP for conditional testing and the probabilistic sequential observability SOR for random testing. Under an assumption that the change to be propagated occurs only in a single time frame, all these three types of observabilities are used.

#### Example 6

Calculate the deterministic observability SOD(y, x). According to the 1st and 2nd steps of Algorithm 7, we find  $M_1 = SC(S=0)$  and  $M_2 = SC(S=2)$ . According to the 3rd step of Algorithm 7 and Algorithm 4 for calculating deterministic sequential controllabilities, we find

$$SOD(y, x) = \min\{SCD(S = 0), SCD(S = 2)\} = \min\{1, 2\} = 1.$$

### Conclusions

In this paper, we have presented a new general approach to testability analysis applicable for sequential and combinational circuits specified at higher functional level. The primary use of the developed testability measures will be in the evaluation of various designs in the early design phase. As the measures are defined at the higher level compared to the gate level, they can be used early in the design process, before the final implementation is available.

Compared to the known work on testability analysis, two types of new results have been achieved. First, a new technique for testability calculation has been proposed. Second, a new view on testability measures together with possibility of exploring additional features and relationships between different measures was presented.

The new technique for testability analysis developed in the paper is based on alternative graphs which allow a uniform representation of both combinational and sequential circuits. Known methods for testability calculation are based on different models for these types of circuits, in particular, binary decision diagrams for combinational circuits and state tables for sequential circuits, and therefore they require different techniques and algorithms for their calculation. The algorithms developed for testability calculation are general in regard to different testability measures. It was shown how these algorithms can be modified when changing the measure or introducing new measures. A general expression for the combinational controllability was developed and the relationships between different measures were explored.

It was shown that testability measures cannot be treated independently of a chosen test method (random or deterministic, conditional or unconditional). A hierarchy of sequential controllabilities for different testing methods was established, where the controllability for random testing is based on the controllability for conditional testing and the latter, in its turn, is based on the controllability of unconditional deterministic testing. It was shown that the algorithms developed for  $\mathcal{AG}s$  are very similar for the cases of combinational and sequential testability measures.

#### References

- AKERS, S. B. (1978): Binary Decision Diagrams. *IEEE Trans. on Comp.*, Vol. 27, pp. 509-516.

- CHEN, C. H. MENON, P. R. (1989): An Approach to Functional Level Testability Analysis. 1989 International Test Conference, Washington, DC, August 29-31, 1989, pp. 373-377.

- GOLDSTEIN, L. H. (1979): Controllability/Observability Analysis. *IEEE Trans. Circuits* Syst., Vol. CAS-26, No. 26, pp. 685-693.

- HAMIDA, B. N. KAMINSKA, B. (1991): Hierarchical Functional Level Testability Analysis. 1991 European Test Conference, Munich, April 10-12, 1991, pp. 327-332.

- UBAR, R. (1976): Test Generation for Digital Circuits Using Alternative Graphs. Proc. of Technical University Tallinn, Estonia, No. 409, pp. 75-81 (in Russian).

- UBAR, R. (1983): Test Pattern Generation for Digital Systems on the Vector Alternative Graph Model. 13th Int. Conf. Fault Tolerant Computing, Milano, 1983, pp. 374-377.

- UBAR, R. KUCHCINSKI, K. (1992): Functional Level Controllability Analysis for Digital Circuits. Design Automation Conf., Kaunas, June 2-4, 1992, pp. 13-21.